Exploring CGA Wait States

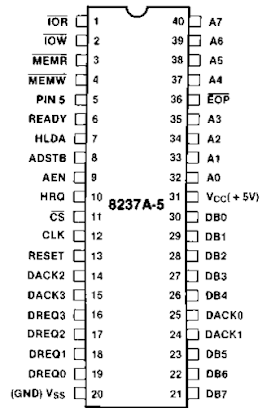

In order to accurately emulate cycle-counted demo effects such as the Kefrens bars effect in 8088MPH, or the end credits in Area 5150, there are essentially four prerequisites: Cycle-accurate 8088 CPU emulation including processor instruction queue emulation Cycle-accurate CGA CRTC emulation Accurate DMA emulation for DRAM refresh Accurate CGA wait state emulation Item #3 was covered in my last blog entry . This article will discuss the last item, CGA wait state emulation. ISA Peripherals and I/O CH RDY The number of wait states that the CPU inserts on each access to the CGA memory depends on the amount of time that the CGA card suppresses the I/O CH RDY signal, which is on ISA bus pin A10. ISA bus pinout, courtesy Wikipedia This signal reaches the motherboard and is passed through miscellaneous TTL logic (on Sheet 2 of the Technical Reference) to eventually connect to the RDY pin on the 8284 clock generator, which in turn produces the READY signal to the CPU. When READY is low du...